Множитель

SS

x1

00

x2

01

x4

10

x8

11

Индекс

|

IND

|

EAX

|

000

|

EBX

|

011

|

ECX

|

001

|

EDX

|

010

|

ESI

|

110

|

EDI

|

111

|

EBP

|

101

|

Нет

|

100

|

База

|

BBB

|

EAX

|

000

|

EBX

|

011

|

ECX

|

001

|

EDX

|

010

|

ESI

|

110

|

EDI

|

111

|

Ofs32(MM=00)/EBP(MM!=00)

|

101

|

ESP

|

100

|

Athlon64

Команды имеют значительное сходство с командами i386, но для работы с шестидесятичетырехразрядными операндами (равно как и с добавленными регистрами R8-R15) команде должен предшествовать префикс REX, четыре младших бита которого используются для указания разрядности операндов (W), расширения слева поля REG байта MOD-REG-R/M (R), поля IND байта SIB (X), поля R/M байта MOD-REG-R/M или поля BBB байта SIB или поля REG кода операции (B). Единица в бите W указывает на использование шестидесятичетырехразрядных операндов. Префикс имеет следующую структуру:

0100

|

W

|

R

|

X

|

B

|

Значения префикса от 0x40 до 0x47 совпадают с однобайтными командами inc и dec процессоров 8086 и i386, так что возможно использование только длинной (с байтом MOD-REG-R/M) формы этих команд.

Если значение шестидесятичетырехразрядной константы может быть записано в четыре байта, старшие четыре байта могут отсутствовать, перед выполнением команды будет выполнено расширение тридцатидвухразрядной константы со знаком или без него. Это в ряде случаев позволяет уменьшить длину команды.

Шестидесятичетырехразрядный адрес может использоваться лишь в нескольких командах (?).

8051

Команды имеют длину от одного до трех байт. При выполнениии арифметических, логических команд и некорорых других команд устанавливаются значения битов регистра состояния PSW (C - перенос, AC - дополнительный перенос, OV - переполнение P - четность, бит нулевого результата отсутствует). PSW также содержит два бита выбора банка регистров (RS1:RS0).

Число команд довольно велико.

PIC10/12/16

Команды имеют фиксированную длину - одно двенадцати- (PIC10) или четырнадцатиразрядное (PIC12/PIC16) слово, состоящее из нескольких полей. Код операции в трех-шести(?) старших битах присутствует всегда, в оставшихся битах в зависимости от команды находятся номер регистра, флаг направления, значение константы или младшие биты адреса перехода. При выполнениии арифметических, логических команд и некорорых других команд устанавливаются значения битов регистра состояния STATUS (C - перенос, DC - дополнительный перенос, Z - ноль). В большинстве моделей длины команды недостаточно для указания регистра, выполнение команды зависит от значения битов выбора банка регистра состояния или регистра выбора банка (это зависит от типа контроллера) . Длины команды также недостаточно для хранения полного адреса, поэтому старшие биты загружаются из регистра PCLATCH, в который они должны быть записаны перед выполнением перехода.

Связь длины команды с обозначением микросхемы по-видимому отсутствует, так что сказанное выше не совсем верно. В частности, микроконтроллеры PIC16F59 в сорокавыводном корпусе PDIP и сорокачетырехвыводном TQFP являются представителями PIC10.

AVR

Команды состоят из одного или двух шестнадцатиразрядных слов, второе слово содержит адрес данных, адрес перехода или его часть. При выполнениии арифметических, логических команд и некорорых других команд устанавливаются значения битов регистра состояния SREG (C - перенос, Z - ноль, N - отрицательное значение, V - переполнение, S - знак, H - дополнительный перенос). Значение флага S устанавливается равным единице при несовпадении значений флагов N и V, и нулю при совпадении. Наличие этого дополнительного флага делает достаточной зависимость команд условных переходов только от одного флага регистра состояния.

[8001]

Вымышленный восьмиразрядный микроконтроллер, реализованный на отладочной плате FPGA Cyclone IV. Все команды имеют длину 1 байт - предпоагалось, что это упростит реализацию. Память программ и память данных могут иметь объем до 64 килобайт каждая, первые 256 байт памяти данных могут использоваться как адресуемый регистром S стек. 8 портов ввода/вывода находятся в своем адресном пространстве.

Арифметические операции выполняются над парами регистров B/D и C/E, в разных вариантах реализации результат операции помещается в регистр A и/или в первый регистр пары (из-за не слишком обоснованного желания не выполнять в одном такте чтение из регистра и запись в него же). Используемая пара регистров определяется одним битом команды. Из-за того-же желания не изменять читаемый регистр был вариант, в котором команды инкремена и декремента записывали измененное значение регистра в регистр А и изменить значение в самом регистре можно было с помощью последующей команы пересылки (mov). Это все можно обойти введением дополнительного скрытого от программиста регистра, да и проблема изменения читаемого регистра существует только если он построен на защелках (latch). Двухступенчатые триггеры свободны от этого недостатка.

Обращения к памяти, переходы и вызовы подпрограмм только косвенные, в качестве индекса используется пара регистров HL. Одна команда может читать или записывать только один байт.

Из 256 кодов команд не используются 12 из группы команд переходов - добавление каких-то новых команд может потребовать отказа от реализованых. Восемь бит на код команд это очень мало и не зря во многих микроконтроллерах используются более длинные коды.

Регистры имеют следующие трехразрядные коды:

Регистр

|

Код

|

Примечание

|

B

|

000

|

|

C

|

001

|

|

D

|

010

|

|

E

|

011

|

|

H

|

100

|

|

L

|

101

|

|

A/F

|

110

|

Интерпретация кода зависит от команды

|

S

|

111

|

|

Пары регистров имеют следующие одноразрядные коды:

Пара

|

Код

|

B/D

|

0

|

C/E

|

1

|

ARM

Команды ARM состоят из одного тридцатидвухразрядного слова и содержат ряд полей, в том числе четырехразрядное поле условия. За счет этого любая команда может быть пропущена без использования условного перехода. Также есть поле запрета/разрешения модификации регистра флагов APRS. Команды обработки данных двух- и трехадресные, т.е. два операнда могут быть взяты из двух регистров, а результат помещен в третий.

Большинство команд Thumb не содержат поля условия, вместо него в набор команд Thumb-2 был введен так называемый IT-блок (If-Then-(Else)-блок) - шестнадцатиразрядная команда, определяющая условия выполнения одной-четырех последующих команд. Что касается модификации регистра флагов APRS, то одни инструкции модифицируют его, другие нет и это может быть источником ошибок при написании программ на ассемблере.

Коды условий переходов следующие:

|

COND

|

|

|

eq

|

0000

|

Z=1

|

Результат равен нулю

|

ne

|

0001

|

Z=0

|

Результат не равен нулю

|

cs/hs

|

0010

|

С=1

|

Перенос установлен (higher or same - a выше или равно b, слова ниже и выше предполагают сравнение чисел без знака)

|

cс/lo

|

0011

|

С=0

|

Перенос не установлен

|

mi

|

0100

|

N=1

|

Знак установлен

|

pl

|

0101

|

N=1

|

Знак не установлен

|

vs

|

0110

|

V=1

|

Переполнение установлено

|

vс

|

0111

|

V=0

|

Переполнение не установлено

|

hi

|

1000

|

C=1 & Z=0

|

a выше b

|

ls

|

1001

|

C=0 | Z=1

|

a ниже или равно b

|

ge

|

1010

|

N=V

|

a больше или равно b

|

lt

|

1011

|

N!=V

|

a меньше b

|

gt

|

1100

|

N=V & Z=0

|

a больше b

|

le

|

1101

|

N!=V | Z=1

|

a меньше или равно b

|

MIPS

Команды MIPS состоят из одного тридцатидвухразрядного слова и содержат ряд полей, в старших шести битах размещается код операции, определяющий также один из трех форматов команды. При нулевом коде операции действие определяется младшими шестью битами команды (кодом функции).

Команды передачи данных

IBM System/360

- Загрузка в регистр D двенадцатиразрядной константы. На самом деле это команда загрузки адреса

с нулевыми кодами регистров индекса и базы. Старшие биты регистра D заполняются нулями.

01000001DDDD00000000VVVVVVVVVVVVla D, V(0, 0) - Загрузка в регистр D слова из ячейки памяти с адресом равным сумме значений в регистрах X и B

а также двенадцатиразрядного смещения F. Нулевые значения X и B означают нуль, а не значание

в нулевом регистре. Старшие байты в памяти размещаются перед младшими (big-endian)

01011000DDDDXXXXBBBBFFFFFFFFFFFFl D, F(X, B) - Загрузка в регистр D полуслова из ячейки памяти с адресом равным сумме значений в регистрах X и B

а также двенадцатиразрядного смещения F. Старшие биты D заполняются нулями(?)

01001000DDDDXXXXBBBBFFFFFFFFFFFFlh D, F(X, B) - Запись в ячейку памяти с адресом равным сумме значений в регистрах X и B, а также двенадцатиразрядного

смещения F значения из регистра S

01010000SSSSXXXXBBBBFFFFFFFFFFFFst S, F(X, B) - Запись в ячейку памяти с адресом равным сумме значений в регистрах X и B, а также двенадцатиразрядного

смещения F младших шестнадцати бит из регистра S

01000000SSSSXXXXBBBBFFFFFFFFFFFFsth S, F(X, B) - Запись в ячейку памяти с адресом равным сумме значений в регистрах X и B, а также двенадцатиразрядного

смещения F младших восьми бит из регистра S. Команда чтения байта из памяти отсутствует(?)

01000010SSSSXXXXBBBBFFFFFFFFFFFFstс S, F(X, B) - Запись в регистр D значения из регистра S

00011000DDDDSSSSlr D, S

PDP-11

Все приведенные ниже команды являются модификациями одной команды mov и отличаются только используемыми способами адресации и регистрами. Допустимы и все(?) другие комбинации, например пересылки память-память.

- Загрузка в регистр константы. После выборки первого слова команды программный счетчик (R7) указывает

на константу. В соответствии со способом адресации (R)+, где

R = R7 = PC, происходит выборка из памяти по адресу, хранящемуся в PC(R7), после чего значение в PC увеличивается на 20001010111000RRRValmov #Val, RRR - Загрузка в регистр значения из ячейки памяти, адрес которой является частью команды.

Если B=1, в регистр загружаетя знаковое расширение байта. Аналогично загрузке константы

после выборки первого слова команды программный счетчик (R7) указывает на адрес.

В соответствии со способом адресации @(R)+, где

R = R7 = PC, происходит выборка из памяти слова по адресу, хранящемуся в PC(R7), выборка из памяти по только что выбранному адресу и увеличение значения в PCна 2B001011111000RRRAddrmov @#Addr, RRR - Загрузка в регистр значения из ячейки памяти, адрес которой является суммой константы и значения в регистре.

Если B=1, в регистр загружаетя знаковое расширение байта.

B001110IND000RRRAddrmov Addr(IND), RRR - Запись в ячейку памяти, адрес которой является частью команды, значения из регистра.

Если B=1, записывается только младший байт, в этом случае адрес может быть нечетным

B001000RRR011111Addrmov RRR, @#Addr - Запись в ячейку памяти, адрес которой является суммой константы и значения в регистре, значения из регистра

B001000RRR110INDAddrmov RRR, Addr(IND) - Запись в стек значения из регистра. В соответствии со способом адресации -(R), где

R = R6 = SP, происходит уменьшение значения в SP на 2 и запись значение из регистра по адресу, хранящемуся в SP0001000RRR100110mov RRR, -(SP) - Загрузка в регистр значения из стека. В соответствии со способом адресации (R)+, где

R = R6 = SP, происходит выборка слова из памяти по адресу хранящемуся в SP и увеичение значения в SP на 20001010110000RRRmov (SP)+, RRR

4004

- Загрузка в аккумулятор константы

1101ССССldm C - Загрузка в пару регистров константы (байта), старший полубайт загружается в регистр с четным номером

(на рисунке он слева), младший - в регистр с нечетным

0010PPP0ССССССССfim P, C - Загрузка в пару регистров константы (байта) из выбранной командой src микросхемы ПЗУ. Адрес байта

выбирается из регистровая пара P0, старший полубайт загружается в регистр с четным номером

(на рисунке он слева), младший - в регистр с нечетным

0010PPP1fin P - Загрузка в аккумулятор значения из указанного регистра

1010RRRRld R - Обмен значениями между аккумулятором и указанным регистром

1011RRRRxch R - Установка флага переноса/заема

11111010stc - Сброс флага переноса/заема

11110001clc - Изменение значения флага переноса/заема на противоположное

11110011cmc - Установка линий управления памятью CM_RAM0..CM_RAM3 в соответсвии со значением в аккумулятора

(выбор банка памяти). Значение 0 соответствуют единице на выводе CM_RAM0 и нулю на остальных.

Ненулевое значение приводит к установке нуля на выводе CM_RAM0, значения на выводах CM_RAM1..CM_RAM3

соответствуют трем младшим битам содержимого аккумулятора (1 -> CM_RAM1, 2 -> CM_RAM2, 4 -> CM_RAM3).

Если не использовать дополнительные микросхемы, допустимы только значения 0, 1, 2 и 4.

11111101dcl - Посылка регистрового управления (Send Register Control). Команда предназначена для выбора микросхемы ОЗУ

и ячейки памяти в ней (для последующего обращения к этой ячейке или к расположенному на выбранной микросхеме

порту вывода), а также для выбора микросхемы ПЗУ (для последующего обращения к расположенному на ней порту

ввода-вывода).

0010PPP1src P - Загрузка в аккумулятор значения из ранее выбранной командой src ячейки памяти

11101001rdm - Запись в ранее выбранную командой src ячейку памяти значения из аккумулятора

11100000wrm - Загрузка в аккумулятор значения из порта ввода-вывода ранее выбранной командой src микросхемы ПЗУ

11101010rdr - Запись в порт ввода-вывода ранее выбранной командой src микросхемы ПЗУ значения из аккумулятора

11100010wrr - Запись в порт вывода ранее выбранной командой src микросхемы ОЗУ значения из аккумулятора

11100001wmp

8080

Универсальные команды

- Загрузка в регистр константы (байта)

00DST110Val0mvi Dst, Val - Загрузка в пару регистров константы (слова)

00RP0001Val0Val1lxi Rp, Val - Загрузка в указатель стека константы (слова)

00110001Val0Val1lxi SP, Val - Загрузка в регистр значения из ячейки памяти, адрес которой находится в паре регистров HL

01DST110mov Dst, M - Загрузка в регистр значения из другого регистра

01DSTSRCmov Dst, Src - Запись в ячейку памяти, адрес которой находится в паре регистров HL, значения из регистра

01110SRCmov M, Src - Запись в стек значений из пары регистров и уменьшение указателя SP на 2

11RP0101push Rp - Загрузка в пару регистров значений из стека и увеличение указателя SP на 2

11RP0001pop Rp

Неуниверсальные команды, работающие только с аккумулятором или парой регистров HL

- Загрузка в аккумулятор значения из ячейки памяти с указанным адресом Addr

00111010Addr0Addr1lda Addr - Загрузка в пару регистров HL значений из пары ячеек памяти с указанным адресом Addr

(в L загружается значение из ячейки с адресом Addr, в H - из ячейки с адресом Addr + 1)

00111010Addr0Addr1lhld Addr - Обмен значениями в парах регистров HL и DE

11101011xchg - Запись в ячейку памяти с указанным адресом Addr значения из аккумулятора

00110010Addr0Addr1sta Addr - Запись в пару ячеек памяти с указанным адресом Addr значений из пары регистров HL

(в ячейку с адресом Addr записывается значение из L, в ячейку с адресом Addr + 1 - значение из H)

00100010Addr0Addr1shld Addr

6502

Вторая тройка бит определяет способ адресации. Если получателем или источником данных является индексный регистр X или Y, он сам не может использоваться в качестве индекса и косвенные способы формирования адреса (NDX и NDY) недоступны. Помещаться в стек могут только значения из аккумулятора и регистра состояния, извлекаемые из стека значения могут помещаться только в эти два регистра. Два младших бита кода команды определяют регистр (?). В ассемблерной записи получатель и источник данных указывается в мнемонике, а не в операнде, поэтому команд довольно много.

- Загрузка в аккумулятор константы (байта)

10101001Val0lda #Val - Загрузка в регистр X константы (байта)

10100010Val0ldx #Val - Загрузка в регистр Y константы (байта)

10100000Val0ldy #Val - Загрузка в аккумулятор значения из ячейки памяти

10101101Addr0Addr1lda Addr - Загрузка в регистр X значения из ячейки памяти

10101110Addr0Addr1ldx Addr - Загрузка в регистр Y значения из ячейки памяти

10101100Addr0Addr1ldy Addr - Загрузка в аккумулятор значения из ячейки памяти, адрес которой является суммой извлекаемого из двух байт в нулевой странице адреса и значения в регистре Y

10110001Addr0lda (Addr), Y - Запись в ячейку памяти значения из аккумулятора

10001101Addr0Addr1sta Addr - Запись в ячейку памяти значения из регистра X

10001110Addr0Addr1stx Addr - Запись в ячейку памяти значения из регистра Y

10001100Addr0Addr1sty Addr - Запись в ячейку памяти, адрес которой является суммой извлекаемого из двух байт в нулевой странице адреса и значения в регистре Y, значения из аккумулятора

10010001Addr0sta (Addr), Y - Загрузка в аккумулятор значения из регистра X

10001010txa - Загрузка в регистр X значения из аккумулятора

10101010tax - Загрузка в аккумулятор значения из регистра Y

10011000tya - Загрузка в регистр Y значения из аккумулятора

10101000tay - Запись в стек значения из аккумулятора и уменьшение значения S на единицу

01001000pha - Загрузка в аккумулятор значения из стека и увеличение значения S на единицу

01101000pla

8086

За исключением загрузки константы, операций с портами ввода/вывода и со стеком, второй байт команды - байт MOD-REG-R/M. Приведены только варианты команд, аналогичные командам 8080, прочие варианты получаются заменой значений полей MOD и R/M. Команды чтения из памяти и записи в память отличаются только битом направления D (1-й бит в коде операции).

- Загрузка в регистр константы

1011WDSTVal0[Val1]mov Dst, Val - Загрузка в регистр значения из ячейки памяти с адресом DS:[Addr]

1000101W00DST110Addr0Addr1mov Dst, DS:[Addr] - Загрузка в регистр значения из ячейки памяти с адресом DS:[BX]

1000101W00DST111mov Dst, DS:[BX] - Загрузка в регистр значения из ячейки памяти с адресом DS:[BX+Addr]

1000101W10DST111Addr0Addr1mov Dst, DS:[BX+Addr] - Загрузка в регистр значения из другого регистра

1000101W11DSTSRCmov Dst, Src - Обмен значениями в двух регистрах

1000011W11DSTSRCxchg Dst, Src - Запись в ячейку памяти с адресом DS:[Addr] из регистра

1000100W00SRC110Addr0Addr1mov DS:[Addr], Src - Запись в ячейку памяти с адресом DS:[BX] из регистра

1000100W00SRC111mov DS:[BX], Src - Запись в ячейку памяти с адресом DS:[BX+Addr] из регистра

1000100W10SRC111Addr0Addr1mov DS:[BX+Addr], Src - Ввод байта/слова из порта с номером P от 0 до 255

1110010WPPPPPPPPin AL/AX, P - Ввод байта/слова из порта с номером, находящемся в регистре DX

1110110Win AL/AX, DX - Вывод байта/слова из регистра AL/AX в порт с номером P от 0 до 255

1110011WPPPPPPPPout P, AL/AX - Вывод байта/слова из регистра AL/AX в порт с номером, находящемся в регистре DX

1110111Wout DX, AL/AX - Запись в стек значения из регистра и уменьшение указателя SP на 2

01010SRCpush Src - Загрузка в регистр значеня из стека и увеличение указателя SP на 2

01011DSTpop Dst

i386

Отличия от 8086 в разрядности операндов и в других значениях поля R/M (второй байт всех перечисленных комано, кроме загрузки константы и операций со стеком).

- Загрузка в регистр константы

1011WDSTVal0[Val1Val2Val3]mov Dst, Val - Загрузка в регистр значения из ячейки памяти с адресом DS:[Addr]

1000101W00DST101Addr0Addr1Addr2Addr3mov Dst, DS:[Addr] - Загрузка в регистр значения из ячейки памяти с адресом DS:[EBX]

1000101W00DST011mov Dst, DS:[EBX] - Загрузка в регистр значения из ячейки памяти с адресом DS:[EBX+Addr]

1000101W10DST011Addr0Addr1Addr2Addr3mov Dst, DS:[EBX+Addr] - Загрузка в регистр значения из другого регистра

1000101W11DSTSRCmov Dst, Src - Обмен значениями в двух регистрах

1000011W11DSTSRCxchg Dst, Src - Запись в ячейку памяти с адресом DS:[Addr] из регистра

1000100W00SRC101Addr0Addr1Addr2Addr3mov DS:[Addr], Src - Запись в ячейку памяти с адресом DS:[EBX] из регистра

1000100W00SRC011mov DS:[EBX], Src - Запись в ячейку памяти с адресом DS:[EBX+Addr] из регистра

1000100W10SRC011Addr0Addr1Addr2Addr3mov DS:[EBX+Addr], Src - Запись в стек значения из регистра и уменьшение указателя ESP на 4

01010SRCpush Src - Загрузка в регистр значеня из стека и увеличение указателя ESP на 4

01011DSTpop Dst

Athlon64

Командам, имеющим дело с шестидесятичетырехразрядными регистрами предшествует префикс REX:

- Загрузка в восьмиразрядный регистр константы

10110DSTVal0mov Dst, Val - Загрузка в тридцатидвухразрядный регистр константы. Старшие тридцать два бита

соответствующего шестидесятичетырехразрядного регистра заполняются нулями

10111DSTVal0Val1Val2Val3mov Dst, Val - Загрузка в шестидесятичетырехразрядный регистр тридцатидвухразрядной константы.

Регистр заполняется расширением константы со знаком. Например, константа

FFFFFFFF(-1) будет записана какFFFFFFFFFFFFFFFF01001R0011REG000Val0Val1Val2Val3mov Dst, Val - Загрузка в шестидесятичетырехразрядный регистр константы

01001R0010111DSTVal0Val1Val2Val3Val4Val5Val6Val7mov Dst, Val - Загрузка в восьмиразрядный регистр значения из ячейки памяти с адресом [RBX]

1000101000DST011mov Dst, [RBX] - Загрузка в шестидесятичетырехразрядный регистр значения из ячейки памяти с адресом [RBX]

01001D001000101100DST011mov Dst, [RBX] - Загрузка в шестидесятичетырехразрядный регистр значения из другого регистра

01001D001000101111DSTSRCmov Dst, Src - Обмен значениями в аккумуляторе и шестидесятичетырехразрядном регистре

01001R0010010REGxchg RAX, Reg - Запись в ячейку памяти с адресом [RBX] из восьмиразрядного регистра

1000100000SRC011mov [RBX], Src - Запись в ячейку памяти с адресом [RBX] из шестидесятичетырехразрядного регистра

01001S001000100000SRC011mov [RBX], Src - Запись в стек значения из регистра и уменьшение указателя RSP на 8

01010SRCpush Src - Загрузка в регистр значения из стека и увеличение указателя RSP на 8

01011DSTpop Dst

8051

Команд передачи данных между регистрами и расположенной на кристалле небольшой памятью очень много. Имеются команды, непосредственно изменяющие значения отдельных битов некоторых ячеек памяти и портов, операндом этих команд является восьмиразрядный битовый адрес, пять бит которого преобразуются в адрес ячейки, оставшиеся три - в номер бита.

Некоторые модели содержат дополнительные 128 восьмиразрядных ячеек памяти, для доступа к ним может использоваться только косвенная адресация(т.е. адрес ячейки должен извлекаться из регистра).

Если в системе используется дополнительная микросхема памяти, получателем или источником данных всегда является регистр-аккумулятор A, адресация памяти только косвенная (с использованием регистра-указателя DPTR, или одного из регистров R0, R1) - эти четыре команды не приведены.

- Загрузка в аккумулятор константы

01110100CCCCCCCCmov A, #C - Загрузка в регистр константы

01111RRRCCCCCCCCmov R, #C - Загрузка в регистр-указатель DPTR шестнадцатиразрядной константы

10010000CCCCCCCCCCCCCCCCmov DPTR, #C - Загрузка в указанную ячейку памяти константы

01110101DDDDDDDDCCCCCCCCmov Dst, #C - Загрузка в указанную ячейку памяти (ее адрес извлекается из регистра R) константы

0111011RCCCCCCCCmov @R, #C ;R = R0 или R1 - Загрузка в аккумулятор значения из регистра R

11101RRRmov A, R - Загрузка в регистр R значения из аккумулятора

11111RRRmov R, A - Загрузка в аккумулятор значения из памяти

11100101SSSSSSSSmov A, Src - Загрузка в регистр R значения из памяти

10101RRRSSSSSSSSmov R, Src - Запись в память значения из аккумулятора

11110101DDDDDDDDmov Dst, A - Запись в память значения из регистра

10001RRRDDDDDDDDmov Dst, R - Косвенная загрузка в аккумулятор значения из памяти

1110011Rmov A, @R ;R = R0 или R1 - Косвенная запись в память значения из аккумулятора

1111011Rmov @R, A ;R = R0 или R1 - Копирование значения в одну ячейку памяти из другой

10000101DDDDDDDDSSSSSSSSmov Dst, Src - Копирование значения в одну ячейку памяти из другой (ее адрес извлекается из регистра R)

1000011RDDDDDDDDmov Dst, @R ;R = R0 или R1 - Копирование значения в одну ячейку памяти (ее адрес извлекается из регистра R) из другой

1010011RSSSSSSSSmov @R, Src ;R = R0 или R1 - Косвенная загрузка значения из памяти программы в аккумулятор (адрес ячейки-источника равен сумме значений в регистре-указателе DPTR и аккумуляторе)

10010011movс A, @A + DPTR - Косвенная загрузка значения из памяти программы в аккумулятор (адрес ячейки-источника равен сумме значений в счетчике команд PC и аккумуляторе)

10000011movс A, @A + PC - Запись значения из указанной ячейки памяти в стек. Значение в SP увеличивается на единицу перед записью

11000000SSSSSSSSpush Src - Запись в указанную ячейку памяти значения из стека. Значение в SP уменьшается на единицу после записи

11010000DDDDDDDDpop Dst - Установка бита ячейки памяти или порта (запись единицы)

11000011BBBBBBBBclr BitAddr - Сброс бита ячейки бамяти или порта (запись нуля)

11010011BBBBBBBBsetb BitAddr - Инверсия бита ячейки бамяти или порта (изменение значения на противоположное)

10110010BBBBBBBBcpl BitAddr

PIC10

- Очистка рабочего регистра WREG (запись нуля)

000001000000clrw - Очистка регистра F (запись нуля)

0000011FFFFFclrf F - Загрузка в рабочий регистр WREG константы

1100CCCCCCCCmovlw C - Копирование содержимого рабочего регистра WREG в регистр

0000001FFFFFmovwf F - Копирование содержимого регистра в рабочий регистр WREG

0010000FFFFFmovf F, 0 - Копирование содержимого регистра в него же (с целью установки флага нуля Z)

0010001FFFFFmovf F, 1 - Перестановка полубайтов в регистре F, результат сохраняется в рабочем регистре WREG (D = 0) или F (D = 1)

001110DFFFFFswapf F, D - Сброс бита B в регистре F

0100BBBFFFFFbcf F, B - Установка бита B в регистре F

0101BBBFFFFFbsf F, B - Копирование содержимого рабочего регистра WREG в регистр OPTION (своего адреса он не имеет)

000000000010option - Копирование содержимого рабочего регистра WREG в регистр управления выходами TRIS (своего адреса он не имеет). F - адрес соответствующего порта ввода/вывода(?)

000000000FFFtris F

PIC12/16

- Очистка рабочего регистра WREG (запись нуля, биты XXXXXXX могут быть любыми(?))

0000010XXXXXXXclrw - Очистка регистра F (запись нуля)

0000011FFFFFFFclrf F - Загрузка в рабочий регистр WREG константы (биты XX могут быть любыми(?))

1100XXCCCCCCCCmovlw C - Копирование содержимого рабочего регистра WREG в регистр (TODO Старший бит младшего байта был 0)

0000001FFFFFFFmovwf F - Копирование содержимого регистра в рабочий регистр WREG

0010000FFFFFFFmovf F, 0 - Копирование содержимого регистра в него же (с целью установки флага нуля Z)

0010001FFFFFFFmovf F, 1 - Сброс бита B в регистре F

0100BBBFFFFFFFbcf F, B - Установка бита B в регистре F

0101BBBFFFFFFFbsf F, B

AVR

- Загрузка в регистр с номером D + 16 константы C (загрузка в регистры R0 - R15 невозможна)

1110CCCCDDDDCCCCldi D, C - Загрузка в регистр R0 байта из памяти программ, на коротый указывает пара индексных регистров R31:R30 (Z)

10010101110X1000lpm - Загрузка в регистр D содержимого регистра S

001011SDDDDDSSSSmov D, S - Загрузка в регистр D значения из порта P

10110PPDDDDDPPPPout P, S - Копирование содержимого регистра S в порт P

10111PPSSSSSPPPPout P, S - Загрузка в регистр D указанного байта из ОЗУ

1001000DDDDD0000AAAAAAAAAAAAAAAAlds D, A - Загрузка в регистр D байта ОЗУ, на коротый указывает пара индексных регистров R27:R26 (X), имеются аналогичные команды, использующие две другие пары индексных регистров, имеются команды, выполняющие постинкремент и преддекремент индекса

1001000DDDDD1100ld D, X - Запись значения из регистра S в указанный байт ОЗУ

1001001SSSSS0000AAAAAAAAAAAAAAAAsts A, S - Запись значения из регистра S в байт ОЗУ, на коротый указывает пара индексных регистров R27:R26 (X), имеются аналогичные команды, использующие две другие пары индексных регистров, имеются команды, выполняющие постинкремент и преддекремент индекса

1001001DDDDD1100st X, S

[8001]

- Загрузка в младшие четыре бита регистра A константы. Старшие четыре бита обнуляются

1000CCCCll A, C - Загрузка в старшие четыре бита регистра A константы. Младшие четыре бита не изменяются

1001CCCClh A, C - Загрузка в регистр DST содержимого регистра SRC

00DSTSRCmov DST, SRC - Запись в память данных байта из регистра SRC

11010SRCst SRC - Загрузка в регистр DST байта из памяти данных

11011DSTld DST - Запись в стек байта из регистра SRC

11000SRCpush SRC - Загрузка в регистр DST байта из стека

11001DSTpop DST - Загрузка в регистр R (регистр B или C) байта из памяти программ

1111111Rlpm R - Запись в порт вывода P значения из регистра A

11100PPPout P, A - Загрузка в регистр A значения из порта ввода P

11101PPPin A, P - Сброс бита B порта вывода P

010PPBBBcb P, B - Установка бита B порта вывода P

011PPBBBsb P, B

ARM/Thumb

- Загрузка в регистр D восьмиразрядной константы. Старшие двадцать четыре бита обнуляются

00100DDDCCCCCCCCmovs D, C - Загрузка в регистр D шестнадцатиразрядной константы. Старшие шестнадцать бит обнуляются

11110C100100CCCC0CCCDDDDCCCCCCCCmovw D, C - Загрузка в старшее полуслово регистра D шестнадцатиразрядной константы. Младшие шестнадцать бит не изменяются. В сочетании с командой movw позволяет загрузить тридцатидвухразрядную константу

11110C101100CCCC0CCCDDDDCCCCCCCCmovt D, C - Загрузка в регистр D тридцатидвухразрядной константы, размещенной в коде программы по адресу

4 * ((PC + 4) / 4 + S)(?). Адрес константы должен быть выровнен по границе слова01001DDDSSSSSSSSldr D, [PC + S] - Загрузка в регистр D тридцатидвухразрядной константы, размещенной в коде программы по адресу

TODO11111000U1011111DDDDSSSSSSSSSSSSldr D, [PC +/- S] - Загрузка в регистр D слова из памяти, адрес которого равен сумме значения в регистре I и беззнакового смещения S

01101SSSSSIIIDDDldr D, [I + S] - Запись значения из регистра R в слово памяти, адрес которого равен сумме значения в регистре I и беззнакового смещения S

01100SSSSSIIIRRRstr R, [I + S] - Запись значения из регистра R в полуслово памяти, адрес которого равен сумме значения в регистре I и беззнакового смещения S

10000SSSSSIIIRRRstrh R, [I + S] - Запись в стек значений из указанных регистров. Единица в бите M означает запись в стек значения LR

1011010MRRRRRRRRpush {REGS} - Извлечение из стека значений указанных регистров. Единица в бите P означает изменение значения PC

1011110PRRRRRRRRpop {REGS}

MIPS

- Загрузка в старшие шестнадцать бит регистра константы. Младшие шестнацать бит обнуляются

00111100000TTTTTIIIIIIIIIIIIIIIIlui $t, i - Загрузка в младшие шестнадцать бит регистра константы. Старшие шестнадцать бит не изменяются. Результат достигается логическим сложением содержимого нулевого регистра и дополненной справа нулями константы

00110100000TTTTTIIIIIIIIIIIIIIIIori $t, $0, i - Копирование значения из регистра s в регистр t. Результат достигается логическим сложением содержимого регистра s и дополненной справа нулями нулевой константы

001101SSSSSTTTTT0000000000000000ori $t, $s, 0 - Загрузка в регистр t слова из памяти. Смещение i знаковое

100011SSSSSTTTTTIIIIIIIIIIIIIIIIlw $t, i($s) - Загрузка в регистр t байта из памяти. Старшие двадцать четыре бита заполняются значением старшего бита загружаемого байта. . Смещение i знаковое

100000SSSSSTTTTTIIIIIIIIIIIIIIIIlb $t, i($s) - Загрузка в регистр t беззнакового байта из памяти. Старшие двадцать четыре бита обнуляются. Смещение i знаковое

100100SSSSSTTTTTIIIIIIIIIIIIIIIIlbu $t, i($s) - Запись в память слова из регистра t. Смещение i знаковое

101011SSSSSTTTTTIIIIIIIIIIIIIIIIsw $t, i($s) - Запись в память младшего байта из регистра t. Смещение i знаковое

101000SSSSSTTTTTIIIIIIIIIIIIIIIIsb $t, i($s)

Команды обработки данных

IBM System/360

- Сложение значения в регистре D со значением в ячейке памяти с адресом равному сумме

значений в регистрах X и B а также двенадцатиразрядного смещения F. Нулевые значения

X и B означают нуль, а не значание в нулевом регистре. Результат помещается в регистр D.

Биты условий в регистре PSW модифицируются

01011010DDDDXXXXBBBBFFFFFFFFFFFFa D, F(X, B) - "Логическое" сложение значения в регистре D со значением в ячейке памяти с адресом равному

сумме значений в регистрах X и B а также двенадцатиразрядного смещения F. Результат помещается

в регистр D. Биты условий в регистре PSW модифицируются

01011110DDDDXXXXBBBBFFFFFFFFFFFFal D, F(X, B) - "Логическое" сложение значения в регистре D со значением в регистре S.

Результат помещается в регистр D. Биты устовий в регистре PSW модифицируются

00011110DDDDSSSSalr D, S - Вычитание из значения в регистре D значения в ячейке памяти с адресом равному сумме

значений в регистрах X и B а также двенадцатиразрядного смещения F. Результат помещается

в регистр D. Биты условий в регистре PSW модифицируются

01011011DDDDXXXXBBBBFFFFFFFFFFFFs D, F(X, B) - "Логическое" вычитание из значения в регистре D значения в ячейке памяти с адресом равному

сумме значений в регистрах X и B а также двенадцатиразрядного смещения F. Результат помещается

в регистр D. Биты условий в регистре PSW модифицируются

01011111DDDDXXXXBBBBFFFFFFFFFFFFsl D, F(X, B) - "Логическое" вычитание из значения в регистре D значения в регистре S.

Результат помещается в регистр D. Биты устовий в регистре PSW модифицируются

00011111DDDDSSSSslr D, S - Умножение значения в регистре D+1 на значение в ячейке памяти с адресом равному сумме

значений в регистрах X и B а также двенадцатиразрядного смещения F. Результат помещается

в регистры D(старшая часть) и D+1(младшая часть). Все числа знаковые. D должен быть четным

01011100DDDDXXXXBBBBFFFFFFFFFFFFm D, F(X, B) - Умножение значения в регистре D+1 на значение в регистре S. Результат помещается

в регистры D(старшая часть) и D+1(младшая часть). Все числа знаковые. D должен быть четным

00011100DDDDSSSSmr D, S - Деление значения в паре регистров D(старшая часть) и D+1(младшая часть) на значение в ячейке памяти

с адресом равному сумме значений в регистрах X и B а также двенадцатиразрядного смещения F. Результат

помещается в регистры D(остаток) и D+1(частное). Все числа знаковые. D должен быть четным

01011101DDDDXXXXBBBBFFFFFFFFFFFFd D, F(X, B) - Деление значения в паре регистров D(старшая часть) и D+1(младшая часть) на значение регистре S.

Результат помещается в регистры D(остаток) и D+1(частное). Все числа знаковые. D должен быть четным

00011101DDDDSSSSdr D, S

PDP-11

В эту группу входят сложение, вычитание, битовые операции И, ИЛИ, исключающее ИЛИ и сдвиги на один разряд. Команды умножения и деления отсутствуют (только в младших моделях?).

- Сложение значений в двух регистрах (SRC и DST) и запись результата во второй из них (DST)

0110000SRC000DSTadd DST, SRC - Вычитание значения в регистре SRC из значение в регистре DST и запись результата в DST

0110000SRC000DSTsub DST, SRC

4004

Первый операнд выбирается из аккумулятора, второй (если есть) - из регистра или из памяти, результат помещается в аккумулятор. В эту группу входят сложение, вычитание, и сдвиги на один разряд. Команды битовых операций, умножения и деления отсутствуют.

- Сложение значения в аккумуляторе со значением в указанном регистре и флагом переноса

1000RRRRadd R - Вычитание из значения в аккумуляторе значения в указанном регистре и флага переноса/заема.

Устанавливает флаг переноса/заема, если заем не требуется(?)

1001RRRRsub R - Увеличение значения в аккумуляторе на единицу

11110010iac - Уменьшение значения в аккумуляторе на единицу

11111000dac

8080

Команды обработки байтов

Основные команды, первый операнд выбирается из аккумулятора, второй (если есть) - из регистра или из памяти, результат помещается в аккумулятор. В эту группу входят сложение, вычитание, битовые операции И, ИЛИ, исключающее ИЛИ и сдвиги на один разряд. Команды умножения и деления отсутствуют.

- Сложение значений в аккумуляторе и регистре

10000SRCadd Src - Сложение значений в аккумуляторе и регистре с учетом переноса

10001SRCadc Src - Вычитание из значения в аккумуляторе значения в регистре

10010SRCsub Src - Вычитание из значения в аккумуляторе значения в регистре с заемом

10011SRCsbb Src

Дополнительные команды, работающие с парами регистров

- Сложение значений в паре регистров HL и другой паре регистров, результат помещается в HL

00RP1001dad Rp - Увеличение значения в паре регистров на единицу

00RP0011inx Rp - Уменьшение значения в паре регистров на единицу

00RP1011dcx Rp

6502

При выполнении большинства команд первый операнд выбирается из аккумулятора, результат помещается в аккумулятор. В отличие от ряда других процессоров перед выполнением сложения и вычитания признак переноса должен быть явно установлен или сброшен. Как и в 8080 команды умножения и деления отсутствуют. В командах, работающих с памятью, вторая тройка бит определяет способ формирования адреса. Приведенные команды оращаются к ячейке памяти в нулевой странице.

- Сложение значений в аккумуляторе и константы с учетом переноса (A = A + V + C)

01101001Val0adc #Val - Сложение значений в аккумуляторе и ячейке памяти с учетом переноса (A = A + M + C)

01100101Addr0adc Addr - Вычитание из значения в аккумуляторе константы с учетом переноса (A = A + !V + C)

11101001Val0sbc #Val - Вычитание из значения в аккумуляторе значения в ячейке памяти с учетом переноса (A = A + !M + C)

11100101Addr0sbc Addr - Сброс признака переноса

00011000clc - Установка признака переноса

00111000sec - Увеличение значения в ячейке памяти на единицу

11100110Addr0inc Addr - Уменьшение значения в ячейке памяти на единицу

11000110Addr0dec Addr - Увеличение значения в регистре X на единицу

11101000inx - Уменьшение значения в регистре X на единицу

11001010dex - Увеличение значения в регистре Y на единицу

11001000iny - Уменьшение значения в регистре Y на единицу

10001000dey

8086

В эту группу входят арифметические операции, битовые операции И, ИЛИ, исключающее ИЛИ и сдвиги. Во всех командах расположение первого операнда и результата совпадают. За исключением команд умножения и деления это может быть как регистр, так и ячейка памяти. Первый операнд команды умножения всегда AX или AL, деления - DX:AX или AH:AL, результат - DX:AX или AH:AL. При делении в DX или AH помещается остаток.

- Сложение значений в регистрах

0000001W11DSTSRCadd Dst, Src - Вычитание значений в регистрах

0010101W11DSTSRCsub Dst, Src - Умножение беззнаковое

1111011W11100SRCmul Src - Деление беззнаковое

1111011W11110SRCdiv Src - Увеличение значения в шестнадцатиразрядном регистре на единицу

01000REGinc Reg - Уменьшение значения в шестнадцатиразрядном регистре на единицу

01001REGdec Reg

i386

- Сложение значений в регистрах

0000001W11DSTSRCadd Dst, Src - Вычитание значений в регистрах

0010101W11DSTSRCsub Dst, Src - Умножение беззнаковое

1111011W11100SRCmul Src - Деление беззнаковое

1111011W11110SRCdiv Src - Увеличение значения в тридцатидвухразрядном регистре на единицу

01000REGinc Reg - Уменьшение значения в тридцатидвухразрядном регистре на единицу

01001REGdec Reg

Athlon64

Команды обработки шестидесятичетырехразрядных данных такие же, как и тридцатидвухразрядных, но им предшествует префикс REX:

- Сложение значений в шестидесятичетырехразрядных регистрах

01001D0S0000001111DSTSRCadd Dst, Src - Вычитание значений в шестидесятичетырехразрядных регистрах

01001D0S0010101111DSTSRCsub Dst, Src - Умножение беззнаковое

0100100S1111011111100SRCmul Src - Деление беззнаковое

0100100S1111011111110SRCdiv Src - Увеличение значения в шестидесятичетырехразрядном регистре на единицу

0100100R1111111111000REGinc Reg - Уменьшение значения в шестидесятичетырехразрядном регистре на единицу

0100100R1111111111001REGdec Reg

8051

- Сложение значений в аккумуляторе и регистре R, результат записывается в аккумулятор

00101RRRadd A, R ;[A] = [A] + [R] - Сложение с переносом значений в аккумуляторt и регистре R, результат записывается в аккумулятор

00111RRRaddc A, R ;[A] = [A] + [R] + [C] - Вычитание с заемом значения в регистре R из значения в аккумуляторе, результат записывается в аккумулятор

10011RRRsubb A, R ;[A] = [A] - [R] - [C] - Беззнаковое умножение значений в аккумуляторе и регистре B, результат записывается в них же (старший байт - в B)

10100100mul AB - Беззнаковое деление значения в аккумуляторе на значение а регистре B, результат записывается в них же (остаток - в B)

10000100div AB

PIC10

- Сложение содержимого рабочего регистра WREG с содержимым регистра F, результат сохраняется в WREG

0001110FFFFFaddwf F, 0 - Сложение содержимого рабочего регистра WREG с содержимым регистра F, результат сохраняется в регистре F. Команда отличается от предыдущей только битом направления (1 вместо 0)

0001111FFFFFaddwf F, 1 - Вычитание содержимого рабочего регистра WREG из содержимого регистра F, результат сохраняется в WREG

0000100FFFFFsubwf F, 0 - Вычитание содержимого рабочего регистра WREG из содержимого регистра F, результат сохраняется в регистре. Команда отличается от предыдущей только битом направления (1 вместо 0)

0000101FFFFFsubwf F, 1 - Прибавление единицы к содержимому регистра F, результат сохраняется в рабочем регистре WREG (D=0) или регистре F (D=1)

001010DFFFFFincf F, D - Вычитание единицы из содержимого регистра F, результат сохраняется в рабочем регистре WREG (D=0) или регистре F (D=1)

000011DFFFFFdecf F, D - Инверсия содержимого регистра F, результат сохраняется в рабочем регистре WREG (D=0) или регистре F (D=1)

001001DFFFFFcomf F, D - Циклический сдиг влево через перенос содержимого регистра F, результат сохраняется в WREG (D = 0) или F (D = 1)

001101DFFFFFrlf F, D - Циклический сдиг вправо через перенос содержимого регистра F, результат сохраняется в WREG (D = 0) или F (D = 1)

001100DFFFFFrrf F, D - Логическое сложение содержимого рабочего регистра WREG и содержимого регистра F, результат сохраняется в WREG (D = 0) или F (D = 1)

000100DFFFFFiorwf F, D - Логическое умножение содержимого рабочего регистра WREG и содержимого регистра F, результат сохраняется в WREG (D = 0) или F (D = 1)

000101DFFFFFandwf F, D - Исключащее ИЛИ содержимого рабочего регистра WREG и содержимого регистра F, результат сохраняется в WREG (D = 0) или F (D = 1)

000110DFFFFFxorwf F, D - Логическое сложение содержимого рабочего регистра WREG и константы. Результат помещается в рабочий регистр

1101CCCCCCCCiorlw C - Логическое умножение содержимого рабочего регистра WREG и константы. Результат помещается в рабочий регистр

1110CCCCCCCCandlw C - Исключающее ИЛИ содержимого рабочего регистра WREG и константы. Результат помещается в рабочий регистр

1111CCCCCCCCxorlw C

PIC12/16

- Сложение содержимого рабочего регистра WREG с константой, результат сохраняется в WREG (бит X может быть любым(?))

11111XCCCCCCCCaddlw C - Сложение содержимого рабочего регистра WREG с содержимым регистра F, результат сохраняется в WREG

0001110FFFFFFFaddwf F, 0 - Сложение содержимого рабочего регистра WREG с содержимым регистра F, результат сохраняется в регистре F. Команда отличается от предыдущей только битом направления (1 вместо 0)

0001111FFFFFFFaddwf F, 1 - Вычитание содержимого рабочего регистра WREG из константы, результат сохраняется в WREG (бит X может быть любым(?))

11110XCCCCCCCCsublw C - Вычитание содержимого рабочего регистра WREG из содержимого регистра F, результат сохраняется в WREG

0000100FFFFFFFsubwf F, 0 - Вычитание содержимого рабочего регистра WREG из содержимого регистра F, результат сохраняется в регистре. Команда отличается от предыдущей только битом направления (1 вместо 0)

0000101FFFFFFFsubwf F, 1 - Прибавление единицы к содержимому регистра F, результат сохраняется в рабочем регистре WREG (D=0) или регистре F (D=1)

001010DFFFFFFFincf F, D - Вычитание единицы из содержимого регистра F, результат сохраняется в рабочем регистре WREG (D=0) или регистре F (D=1)

000011DFFFFFFFdecf F, D - Логическое сложение содержимого рабочего регистра WREG и содержимого регистра F, результат сохраняется в WREG (D = 0) или F (D = 1)

000100DFFFFFFFiorwf F, D - Логическое умножение содержимого рабочего регистра WREG и содержимого регистра F, результат сохраняется в WREG (D = 0) или F (D = 1)

000101DFFFFFFFandwf F, D - Исключащее ИЛИ содержимого рабочего регистра WREG и содержимого регистра F, результат сохраняется в WREG (D = 0) или F (D = 1)

000110DFFFFFFFxorwf F, D

AVR

- Сложение содержимого регистра D с содержимым регистра S, результат сохраняется в регистре D

000011SDDDDDSSSSadd D, S - Сложение содержимого регистра D с содержимым регистра S и переносом, результат сохраняется в регистре D

000111SDDDDDSSSSadc D, S - Вычитание содержимого регистра S из содержимого регистра D, результат сохраняется в регистре D

000110SDDDDDSSSSsub D, S - Вычитание содержимого регистра S и переноса из содержимого регистра D, результат сохраняется в регистре D

000010SDDDDDSSSSsbc D, S - Беззнаковое умножение содержимого регистра S на содержимое регистра R, результат сохраняется в паре регистров R1:R0

100111SRRRRRSSSSmul R, S - Логическое сложение (ИЛИ) значений в двух регистрах и запись результата в первый из них (D)

001010SDDDDDSSSSor D, S - Логическое умножение (И) значений в двух регистрах и запись результата в первый из них (D)

001000SDDDDDSSSSand D, S - Вычисление функции несовпадения (исключающего ИЛИ) значений в двух регистрах и запись результата в первый из них (D)

001001SDDDDDSSSSeor D, S - Вычитание константы из содержимого регистра D + 16, результат сохраняется в том же регистре D + 16

0101CCCCDDDDCCCCsubi D, C - Логическое сложение (ИЛИ) содержимого регистра D + 16 с константой, результат сохраняется в том же регистре D + 16

0110CCCCDDDDCCCCori D, C - Логическое умножение (ИЛИ) содержимого регистра D + 16 на константу, результат сохраняется в том же регистре D + 16

0111CCCCDDDDCCCCandi D, C - Сложение содержимого пары регистров 2*D+25:2*D+24 с шестиразрядной константой, результат сохраняется в этих же регистрах

10010110ССDDССССadiw D, C - Вычитание шестиразрядной константы из содержимого пары регистров 2*D+25:2*D+24, результат сохраняется в этих же регистрах

10010111ССDDССССsbiw D, C

[8001]

Во всех командых DST и SRC могут быть только B/D или C/E.

- Увеличение на единицу значения в регистре

10111REGinc REG - Уменьшение на единицу значения в регистре

10110REGdec REG - Сложение значений в паре регистров

1111000Padd DST, SRC - Сложение значений в паре регистров и флага переноса

1111001Padс DST, SRC - Вычитание значения во втором регистре пары из значения в первом

1111010Psub DST, SRC - Вычитание значения во втором регистре пары из значения в первом с учетом переноса

1111011Psbb DST, SRC - Битовое умножение значений в паре регистров

1111100Pand DST, SRC - Битовое сложение значений в паре регистров

1111101Por DST, SRC - Вычисление функции несовпадения битов значений в паре регистров

1111110Pxor DST, SRC

ARM/Thumb

- Сложение константы со значением в регистре R и запись результата в этот же регистр

00110RRRCCCCCCCCadds R, C - Вычитание константы из значения в регистре R и запись результата в этот же регистр

00111RRRCCCCCCCCsubs R, C - Сложение значений в двух регистрах и запись результата в третий (DST)

0001100MMMNNNDSTadds D, N, M - Вычитание значения одного регистра (MMM) из значения другого (NNN) и запись результата в третий (DST)

0001100MMMNNNDSTsubs D, N, M - Логическое сложение значений в двух регистрах и запись результата в первый из них (DST)

0100001100SRCDSTorrs D, S - Логическое умножение значений в двух регистрах и запись результата в первый из них (DST)

0100000000SRCDSTands D, S - Вычисление функции несовпадения (исключающего ИЛИ) значений в двух регистрах и запись результата в первый из них (DST)

0100000001SRCDSTeors D, S

MIPS

- Сложение значений в двух регистрах ($s и $t) и запись результата в третий ($d), при переносе происходит исключение

000000SSSSSTTTTTDDDDD00000100000add $d, $s, $t - Сложение значений в двух регистрах ($s и $t) и запись результата в третий ($d), перенос игнорируется. Почему-то команда называется add unsigned

000000SSSSSTTTTTDDDDD00000100000addu $d, $s, $t - Вычитание значения в регистре $t из значения в регистре $s и запись результата в регистр $d, при заеме происходит исключение

000000SSSSSTTTTTDDDDD00000100010sub $d, $s, $t - Вычитание значения в регистре $t из значения в регистре $s и запись результата в регистр $d, заем игнорируется

000000SSSSSTTTTTDDDDD00000100011subu $d, $s, $t - Сложение значений в двух регистрах $s и $t со знаковой константой и запись результата во второй из них, при переносе происходит исключение

001000SSSSSTTTTTIIIIIIIIIIIIIIIIaddi $t, $s, I - Сложение значений в двух регистрах $s и $t со знаковой константой и запись результата во второй из них, перенос игнорируется

001001SSSSSTTTTTIIIIIIIIIIIIIIIIaddiu $t, $s, I

Команды передачи управления

IBM System/360

- Условный переход по адресу равному сумме значений в регистрах X и B а также

двенадцатиразрядного смещения F. Нулевые значения X и B означают нуль, а не значание

в нулевом регистре. Переход выполняется если поле MASK соответствует битам условий

в регистре PSW. Старшие байты в памяти размещаются перед младшими (big-endian)

01000111MASKXXXXBBBBFFFFFFFFFFFFbc M, F(X, B) - Безусловный переход по адресу равному сумме значений в регистрах X и B а также

двенадцатиразрядного смещения F. Нулевые значения X и B означают нуль, а не значание

в нулевом регистре. Это та же команда условного перехода, поле MASK которой содержит все единицы

010001111111XXXXBBBBFFFFFFFFFFFFb F(X, B) - Условный переход по адресу, содержащемуся в регистре X. Переход выполняется если

поле M соответствует битам условий в регистре PSW

00000111MASKXXXXbcr M, X - Безусловный переход по адресу, содержащемуся в регистре X. Команда может

также использоваться для возврата из подпрограммы

000001111111XXXXbr X - Переход к подпограмме, адрес которой равен сумме значений в регистрах X и B а также

двенадцатиразрядного смещения F. Перед переходом адрес следующей за командой инструкции

сохраняется в регистре L

01000101LLLLXXXXBBBBFFFFFFFFFFFFbal L, F(X, B) - Переход к подпрограмме адрес которой, содержится в регистре X. Перед переходом

адрес следующей за командой инструкции сохраняется в регистре L

00000101LLLLXXXXbalr L, X

PDP-11

Условные переходы только относительные, безусловные переходы и переходы к подпрограмме могут быть абсолютными и относительными. Здесь приведены только команды относительных переходов, соответствующие аналогичным командам процессоров 80x86, но есть и более экзотические варианты.

- Условный переход - изменение значения в программном счетчике PC на удвоенное значение смещения при истинности условия

--COND----Ofs---bxx Ofs - Относительный безусловный переход - изменение значения в программном счетчике PC на значение смещения

0000000001110111Ofsjmp Ofs - Относительный переход к подпрограмме - изменение значения в программном счетчике PC на значение смещения

0000100111110111Ofsjsr Ofs - Возврат из подпрограммы

0000000000001111rts R7 - Останов

0000000000000000halt

4004

Во всех командах указываются абсолютные значения адресов, так что перемещение программы из одной области памяти в другую невозможно.

- Условный переход - загрузка в младшие 8 бит счетчика команд адреса AAAAAAAA при истинности условия.

Старшие четыре бита адреса совпадают со старшими четырьмя битами следующей за переходом команды.

0001IZCTAAAAAAAAjcn A ;Переход выполняется при истинности условия (I != 0) ^ ((Z != 0) & (AC = 0)) | ((C != 0) & (CY != 0)) | ((T != 0) & (TEST = 0)) - Безусловный переход - загрузка в счетчик команд указанного адреса AAAAAAAAAAAA

0100AAAAAAAAAAAAjun A - Переход к подпрограмме - сохранение во внутреннем стеке адреса следующей команды и загрузка в счетчик команд указанного адреса AAAAAAAAAAAA

0101AAAAAAAAAAAAjms A - Возврат из подпрограммы - загрузка DDDD в аккумулятор и значения из стека в счетчик команд

1100DDDDbbl DDDD

Комбинированная команда (она одна?)

- Увеличение значения в указанном регистре на единицу и загрузка в младшие 8 бит счетчика команд

адреса AAAAAAAA при ненулевом результате. Старшие четыре бита адреса совпадают со старшими четырьмя

битами следующей за переходом команды.

0111RRRRAAAAAAAAjsz R, A

8080

Во всех командах указываются абсолютные значения адресов, так что перемещение программы из одной области памяти в другую невозможно.

- Условный переход - загрузка в указатель команды PC указанного адреса Addr при истинности условия

11CCC010Addr0Addr1jcc Addr - Безусловный переход - загрузка в указатель команды PC указанного адреса Addr

11000011Addr0Addr1jmp Addr - Переход к подпрограмме - запись адреса следующей команды в стек и загрузка в PC указанного адреса Addr

11001101Addr0Addr1call Addr - Косвенный переход к подпрограмме - запись адреса следующей команды в стек и загрузка в PC содержимого пары регистров HL

11101001pchl - Возврат из подпрограммы - загрузка в PC значения из стека

11001001ret

6502

В командах условных переходов указываются восьмиразрядные смещения относительно начала следующей команды, в командах безусловных переходов и переходов к подпрограмме указываются абсолютные значения адресов, так что перемещение программы из одной области памяти в другую невозможно.

- Условный переход - изменение указателя команды PC на величину смещения Ofs при истинности условия

CCC00000Ofs0bcc Ofs - Безусловный переход - загрузка в указатель команды PC указанного адреса Addr

01001100Addr0Addr1jmp Addr - Переход к подпрограмме - запись адреса из PC в стек и загрузка в PC указанного адреса Addr

00100000Addr0Addr1jsr Addr - Возврат из подпрограммы - загрузка в PC значения из стека

01100000rts

8086

В отличие от процессора 8080 во всех командах указываются не абсолютные адреса переходов, а смещения относительно адреса, следующего за командой. Кроме того, в командах условных переходов смещение может быть только восьмиразрядным, так что диапазон переходов находится в пределах от -128 до 127. Если требуется переход с большим смещением, придется комбинировать условный переход с безусловным.

Все перечисленные ниже команды кроме int выполняют переходы в пределах одного сегмента, т.е. не изменяют значение CS. Команды переходов/вызовов/возвратов в другой сегмент кода также существуют, но в них значение CS задается абсолютно и, соответственно, перемещение программы из одной области памяти в другую невозможно. В системе MS-DOS EXE-файл содержит таблицу перемещений, содержащую адреса, сегментные части которых должны скорректированы перед запуском программы.

- Условный переход - изменение указателя команды IP на величину смещения Ofs

0111CONDOfsjcc Ofs - Безусловный переход

11101001Ofs0Ofs1jmp Ofs - Переход к подпрограмме

11101000Ofs0Ofs1call Ofs - Переход к подпрограмме косвенный, указатель команды IP загружается из регистра BX.

Второй байт команды похож на MOD-REG-R/M, но место REG занимает часть кода операции.

Команда используется для реализации в языках высокого уровня явных или неявных

указателей на функции. По-видимому, процессор 8080 аналогичной команды не имеет (?)

1111111111010111call [BX] - Возврат из подпрограммы - загрузка в IP значения из стека

1100011ret - Вызов прерывания с номером Numb

11001101Numbint Numb

i386

Коды команд не отличаются от кодов аналогичных команд процессора 8086, но вместо шестнадцатиразрядных смещений используются тридцатидвухразрядные. Добавлены команды условных переходов с тридцатидвухразрядным смещением.

- Условный переход - изменение указателя команды IP на величину смещения Ofs

0111CONDOfsjcc Ofs - Условный переход - изменение указателя команды IP на величину тридцатидвухразрядного смещения Ofs

000011111000CONDOfs0Ofs1Ofs2Ofs3jcc Ofs - Безусловный переход

11101001Ofs0[Ofs1Ofs2Ofs3]jmp Ofs - Переход к подпрограмме

11101000Ofs0Ofs1Ofs2Ofs3call Ofs - Переход к подпрограмме косвенный, указатель команды EIP загружается из регистра EBX

Второй байт команды похож на MOD-REG-R/M, но место REG занимает часть кода операции

1111111111010011call [EBX] - Возврат из подпрограммы - загрузка в EIP значения из стека

1100011ret - Вызов прерывания с номером Numb

11001101Numbint Numb

Athlon64

Коды команд не отличаются от кодов аналогичных команд процессора i386, добавлена команда syscall, используемая для вызовов функций ОС вместо int.

- Системный вызов

0000111100000101syscall

8051

- Относительный переход, если содержимое аккумулятора равно нулю

01100000SSSSSSSSjz ofS;Jump if Zero - Относительный переход, если содержимое аккумулятора равно не нулю

01110000SSSSSSSSjnz ofS;Jump if Not Zero - Относительный переход, если указанный бит сброшен (равен нулю). Используется для реализации обычных команд типа переход если выше или равно.

00010000BBBBBBBBSSSSSSSSjbc BitAddr, ofS;Jump if Bit Clear - Относительный переход, если указанный бит установлен (равен единице). Используется для реализации обычных команд типа переход если ниже.

00100000BBBBBBBBSSSSSSSSjb BitAddr, ofS;Jump if Bit set - Безусловный переход

00000010AAAAAAAAAAAAAAAAljmp Addr - Переход к подпрограмме

00010010AAAAAAAAAAAAAAAAlcall Addr - Возврат из подпрограммы

00100010ret

Комбинированные команды

- Уменьшение значения в регистре R на 1 и относительный переход, если результат не равен нулю

11011RRRSSSSSSSSdjnz R, ofS;Decrement and Jump if Not Zero

PIC10

- Пропуск следующей команды если бит B регистра F равен нулю

0110BBBFFFFFbtfsc F, B;Bit Test F and Skip if Clear - Пропуск следующей команды если бит B регистра F равен единице

0111BBBFFFFFbtfss F, B;Bit Test F and Skip if Set - Безусловный переход. В моделях с памятью программ, превышающей 512 слов, старшие биты адреса перехода загружаются из регистра STATUS

101AAAAAAAAAgoto A - Переход к подпрограмме. В моделях с памятью программ, превышающей 256 слов, старшие (10-й и 9-й) биты адреса перехода загружаются из регистра STATUS, 8-й бит обнуляется

1001AAAAAAAAcall A - Возврат из подпрограммы с записью константы в рабочий регистр WREG

1000CCCCCCCCretlw C - Переход в спящий режим

000000000011sleep - Сброс сторожевого таймера. Если таймер включен, при его переполнении происходит сброс контроллера. Чтобы этого не происходило, нужно периодически сбрасывать таймер

000000000100clrwdt - Пустая команда

000000000000nop

Комбинированные команды

- Увеличение значения из регистра F на 1, запись результата в рабочий регистр WREG (D = 0) или регистр (D = 1) и пропуск следующей команды если результат равен нулю

001111DFFFFFincfsz F, D;Increment F and Skip if Zero - Уменьшение значения из регистра F на 1, запись результата в рабочий регистр WREG (D = 0) или регистр (D = 1) и пропуск следующей команды если результат равен нулю

001011DFFFFFdecfsz F, D;Decrement F and Skip if Zero

PIC12/16

- Пропуск следующей команды если бит B регистра F равен нулю

0110BBBFFFFFFFbtfsc F, B;Bit Test F and Skip if Clear - Пропуск следующей команды если бит B регистра F равен единице

0111BBBFFFFFFFbtfss F, B;Bit Test F and Skip if Set - Безусловный переход

101AAAAAAAAAAAgoto A - Переход к подпрограмме

100AAAAAAAAAAAcall A - Возврат из подпрограммы

00000000001000return - Возврат из подпрограммы с записью константы в рабочий регистр WREG (биты XX могут быть любыми(?))

1101XXCCCCCCCCretlw C

Комбинированные команды

- Увеличение значения из регистра F на 1, запись результата в рабочий регистр WREG (D = 0) или регистр (D = 1) и пропуск следующей команды если результат равен нулю

001111DFFFFFFFincfsz F, D;Increment F and Skip if Zero - Уменьшение значения из регистра F на 1, запись результата в рабочий регистр WREG (D = 0) или регистр (D = 1) и пропуск следующей команды если результат равен нулю

001011DFFFFFFFdecfsz F, D;Decrement F and Skip if Zero

AVR

- Пропуск следующей команды если бит B регистра R равен нулю

1111110RRRRR0BBBsbrc R, B;Skip if Bit of R is Clear - Пропуск следующей команды если бит B регистра R равен единице

1111111RRRRR0BBBsbrs R, B;Skip if Bit of R if Set - Пропуск следующей команды если бит B порта вода-вывода P равен нулю

10011001PPPPPBBBsbic P, B;Skip if Bit of Io is Clear - Пропуск следующей команды если бит B порта вода-вывода P равен единице

10011011PPPPPBBBsbis P, B;Skip if Bit of Io is Set - Переход, если бит B в регистре статуса равен нулю. Используется для реализации обычных команд типа переход, если не равно, если больше или равно

111101SSSSSSSBBBbrbc B, ofS - Переход, если бит B в регистре статуса равен единице. Используется для реализации обычных команд типа переход, если равно, если меньше

111100SSSSSSSBBBbrbs B, ofS - Безусловный переход. В микроконтроллерак с памятью 8K байт (4K слов) и меньше отсутствует

1001010AAAAA110AAAAAAAAAAAAAAAAAjmp A - Безусловный переход относительный. В микроконтроллерак с памятью 8K байт (4K слов) и меньше обеспечивает переход из любой точки программы в любую другую

1100SSSSSSSSSSSSrjmp ofS - Переход к подпрограмме. В микроконтроллерак с памятью 8K байт (4K слов) и меньше отсутствует

1001010AAAAA111AAAAAAAAAAAAAAAAAcall A - Переход к подпрограмме относительный. В микроконтроллерак с памятью 8K байт (4K слов) и меньше обеспечивает переход из любой точки программы в любую другую

1101SSSSSSSSSSSSrcall ofS - Переход к подпрограмме, адрес которой находится в паре регистрова R31:R30 (Z)

10010101XXXX1001call A - Возврат из подпрограммы

100101010XX01000ret - Возврат из подпрограммы обработки прерывания

100101010XX11000reti

[8001]

- Условный переход при сброшенном флаге переноса

10100000jnc - Условный переход при установленном флаге переноса

10100001jc - Безусловный переход

10101110jmp - Переход к подпрограмме. Адрес следующей команды сохраняется в паре регистров D/E.

10101111call

ARM/Thumb

- Условный переход

1101CONDSSSSSSSSbcc ofS - It-блок (If-Then-Else-блок) - префикс блока из одной-четырех команд, выполняемых

при истинности/ложности условия. Число команд в блоке определяется полем MASK.

В программе на ассемблере условия указываются в последующих командах и они

должны быть согласованы друг с другом и с префиксом (т.е. совпадать с условием

первой команды для t и быть его отрицанием для e). Команда набора Thumb-2

10111111CONDMASKit{t|e{t|e{t|e}}} - Косвенный безусловный переход по адресу, находящемуся в регистре R. Младший бит определяет набор команд, для Thumb(-2) он должен быть 1. Команда также используется для возврата из подпрограммы

010001110RRRR000bx R - Косвенный переход к подпрограмме, адрес которой находится в регистре R. Младший бит определяет набор команд, для Thumb(-2) он должен быть 1

010001111RRRR000blx R

MIPS

- Переход при отрицательности значения в регистре t. При переходе новое значение pc получается сложением старого со сдвинутым на два разряда влево знаковым смещением Ofs=I

000001SSSSS00000IIIIIIIIIIIIIIIIbltz $t, Ofs - Переход при неотрицательности значения в регистре t. При переходе новое значение pc получается сложением старого со сдвинутым на два разряда влево знаковым смещением Ofs=I. Почему-то код команды отличается от кода команды bltz значением в поле регистра $t, а не значением кода операции (00001 вместо 00000)

000001SSSSS00001IIIIIIIIIIIIIIIIbgez $t, Ofs - Переход при равенстве значений в регистрах s и t. При переходе новое значение pc получается сложением старого со сдвинутым на два разряда влево знаковым смещением Ofs=I

000100SSSSSTTTTTIIIIIIIIIIIIIIIIbeq $s, $t, Ofs - Переход при неравенстве значений в регистрах s и t. При переходе новое значение pc получается сложением старого со сдвинутым на два разряда влево знаковым смещением Ofs=I

000101SSSSSTTTTTIIIIIIIIIIIIIIIIbne $s, $t, Ofs - Переход при отрицательности или равенстве нулю значения в регистре t. При переходе новое значение pc получается сложением старого со сдвинутым на два разряда влево знаковым смещением Ofs=I

000110SSSSS00000IIIIIIIIIIIIIIIIblez $t, Ofs - Переход при положительности значения в регистре t. При переходе новое значение pc получается сложением старого со сдвинутым на два разряда влево знаковым смещением Ofs=I

000111SSSSS00000IIIIIIIIIIIIIIIIbgtz $t, Ofs - Безусловный переход

000010AAAAAAAAAAAAAAAAAAAAAAAAAAj Addr - Косвенный безусловный переход по адресу, хранящемуся в регистре s. Также используется для возврата из подпрограммы

000000SSSSS000000000000000001000jr $s - Безусловный переход с запоминанием адреса следующей команды в регистре ra. Адрес перехода вычисляется по формуле (pc & 0xF0000000) | (addr << 2)

000010AAAAAAAAAAAAAAAAAAAAAAAAAAjal Addr - Косвенный безусловный переход по адресу, хранящемуся в регистре s с запоминанием адреса следующей команды в регистре d

000000SSSSS00000DDDDD00000001001jalr $d, $s

Hello, World!

В соответствии с традицией, первая программа должна вывести на экран приветствие вроде Hello, World! Эта программа очень проста и может быть написана непосредственно в машинном коде. Код зависит от процессора, операционной системы и используемого устройства вывода. В некотором смысле такая программа для микроконтроллера скрывает меньше.

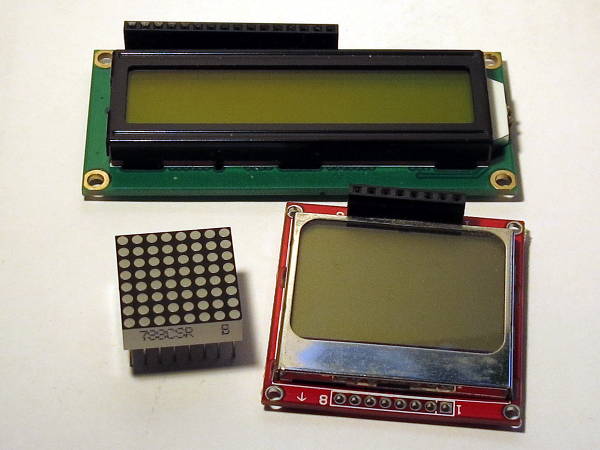

Чтобы выполнить программу необходима соответствующая машина или ее программный эмулятор. Если речь о реальных микроконтроллерах, потребуется некоторое оборудование:

- Программатор

- Микроконтроллер

- Макетная плата

- Набор гибких перемычек

- Набор резисторов

- Светодиоды/Светодиодная матрица

- Кнопки

Можно купить готовую плату с установленными на ней программатором, микроконтроллером и какими-либо периферийными устройствами (как минимум, светодиодом) например, Arduino или STM Nucleo. Также можно купить готовый комплект, содержащий все перечисленное и, возможно, что-то еще.

Если покупать отдельно, можно рекомендовать

- Программатор USBASP V2.0 (для микроконтроллеров AVR)

- Микроконтроллер ATmega328P(DIP28), но подойдут и многие другие

- Или плата Arduino UNO R3/ATmega328P(DIP28)+ATmega16U2

- Макетная плата SYB-120

- Набор резисторов 30 номиналов по 10 штук каждого (от 10 Ом до 1 МОм)

- Светодиодная матрица 8x8 1.9 мм

- Кнопки 6x6x5 мм

Хотя программатор USBASP и дешев, сэкономить не получится, цена программатора и микроконтроллера лишь немного меньше цены китайского клона платы Arduino UNO. К тому же эта плата способна без какого-либо дополнительного оборудования передавать данные на персональный компьютер и принимать их от него. Она также может использоваться как программатор других микроконтроллеров (не только AVR).

Запись программы в контроллер платы Arduino обычно происходит не так, как в отдельно стоящий микроконтроллер и в этом есть некоторая "магия". Часть памяти программ занимает так называемый загрузчик (bootloader) и работа контроллера начинается с исполнения его кода. Если загрузчик обнаруживает попытку записи программы, он предпринимает соответствующие действия, если нет - передает управление основному коду.

Указанная макетная плата представляется более хорошим вариантом, чем другая распространенная плата MB-102, но также не лишена недостатков - шины питания имеющегося у автора экземпляра не обеспечивают надежного контакта с тонкими выводами. Обе платы существенно хуже Wishboard WBU-504, но и намного дешевле.

Из трех сотен резисторов большая часть не понадобится, но при покупке на ebay или aliexpress это, по-видимому, самый дешевый вариант. Резисторы лучше брать углеродистые (бежевые), обозначения на них читаются лучше чем на металлопленочных (синих). Углеродистые резисторы почему-то дороже.

Нельзя покупать светодиодную матрицу 8x8 3 мм - по какой-то причине рассояние между рядами ее выводов (24 мм) не соответствует шагу отверстий на плате (2.54 мм). Матрица 8x8 3.7 мм может быть установлена, но для ее подключения потебуются короткие жесткие перемычки или две макетные платы.

Кнопки 6x6x5 мм по-видимому самые удобные. Кнопки 6x6x4.3 мм чувствуются пальцем хуже.

EDSAC

Предполагается использование эмулятора Edsac Simulator, вывод на телетайп. В реальную машину программа может быть введена с перфоленты, в эмулятор - из текстового файла. Первый вариант программы - простая последовательность команд вывода на телетайп, если понадобится выводить текст другой длины, программу придется полнотью переписать. Второй вариант демонстрирует работу с массивом, для чего используется самомодифицирующийся код и обойтись без этого невозможно.

Важно! Перед нажатием кнопки Start должен быть выбран загрузчик Initial Order 1.

Сразу после загрузки программы она останавливается, ее выполнение может быть продолжено нажатием кнопки Reset или многократного нажатия кнопки Single E.P. во втором случае выполняется одна комана и машина останавливается. На экранах можно видеть содержимое регистров и памяти (нужно выбрать Long Tank 1, содержащий ячейки памяти с 32 до 63).

Если заменить первую команду ZS на XS, останвка произойдет после однократного выполнения программы.

Команды приведены в том виде, в котором они пробиваются на перфоленте - буквенный код команды (один столбец), десятичный адрес операнда (ноль или больше столбцов), бит разрядности операнда/единица младшего разряда (S или D). Двоичные коды команд не приводятся, их можно увидеть на экране.

Первый вариант:

T53S [EOF position]

[32] ZS [hlt]

[33] O45S [prn]

[34] O46S [prn]

[35] O47S [prn]

[36] O48S [prn]

[37] O49S [prn]

[38] O50S [prn]

[39] O51S [prn]

[40] O52S [prn]

[41] ZS [hlt]

[42] T44S [clr Acc]

[43] E33S

[44] 0S [Tmp]

[45] *F [Letter shift]

[46] HS

[47] ES

[48] LS

[49] LS

[50] OS

[51] @S [CR]

[52] &S [LF]

Второй вариант:

T68S [EOF position]

[32] ZS [hlt]

[33] T59S [clr Acc]

[34] A56S [lda Ind0]

[35] T57S [sta Ind]

[36] A55S [lda Cmd]

[37] A57S [add Ind]

[38] T39S [sta Cmd]

[39] AS [lda Ch]

[40] T58S [sta Tmp]

[41] H58S [ldm Tmp]

[42] C54S [and One]

[43] S54S [sub One]

[44] E52S [jns 52]

[45] O58S [prn Tmp]

[46] T58S [clr Acc]

[47] A57S [add Ind]

[48] A54S [add One]

[49] A54S [add One]

[50] T57S [sta Ind]

[51] E36S [jns 36]

[52] ZS [hlt]

[53] E33S [jns 33]

[54] 0D [One]

[55] AS [Add Cmd]

[56] 060S [Ind0]

[57] 0S [Ind]

[58] 0S [Tmp]

[59] *S [Letter shift]

[60] HS

[61] ES

[62] LS

[63] LS

[64] OS

[65] @S [CR]

[66] &S [LF]

[67] 0D [EOS]

PDP-11

Предполагается использование эмулятора simhv/pdp11 без операционной системы, вывод на телетайп. В реальную машину программа может быть введена с помощью пульта (blinkenlight console?), в память эмулятора - с помощью команд

deposit addr, value

Команду можно сократить до первой буквы, адреса и значения должны вводиться в восьмеричной системе счисления (в реальную машину - в двоичной). Запуск эмулятора

go addr

В следующих примерах addr=10008 (020016)

Адрес Код Адрес(8) Код(8) Метка Мнемоника

----- --------- -------- ------------- ------- ---------

0200 15C2 FF74 001000 012702 177564 mov #177564, R2 ;Регистр статуса телетайпа

0204 15C0 0048 001004 012700 000110 mov #'H', R0

0208 9032 0002 001010 110062 000002 @Wait1: movb (R0), 2(R2) ;Запись в регистр данных телетайпа

020C 8BCA 001014 105712 tstb (R2) ;Проверка завершения записи

020E 80FE 001016 100376 bpl @Wait1 ;Если в разряде 7 регистра статуса телетайпа 0 - повторить проверку

0210 15C0 0065 001020 012700 000145 mov #'e', R0

0214 9032 0002 001024 110062 000002 @Wait2: movb (R0), 2(R2)

0218 8BCA 001030 105712 tstb (R2)

021A 80FE 001032 100376 bpl @Wait2

...

0252 0000 001122 000000 halt

В PDP-11 регистры устройств ввода-вывода размещаются в общем адресном пространстве памяти. Соответственно, для управления этими устройствами используются обычные команды передачи данных. Команда tstb выполняет установку разрядов Z и N регистра PS в соответствии со значением операнда. Код содержит тринадцать похожих фрагментов (приведены только первые два), что плохо.

Символы можно выводить в цикле:

Адрес Код Адрес(8) Код(8) Метка Мнемоника

----- --------- -------- ------------- ------- ---------

0200 15C2 FF74 001000 012702 177564 mov #177564, R2 ;Регистр статуса телетайпа

0204 11C1 001004 010701 mov R7, R1

0206 11C1 0014 001006 062701 000024 add R1, #24 ;R1 = @Text

020A 9440 001012 112100 @Loop: movb (R1)+, R0

020C 0305 001014 001405 beq @Exit

020E 9032 0002 001016 110062 000002 @Wait: movb (R0), 2(R2) ;Запись в регистр данных телетайпа

0212 8BCA 001022 105712 tstb (R2) ;Проверка завершения записи

0214 80FE 001024 100376 bpl @Wait ;Если в разряде 7 регистра статуса телетайпа 0 - повторить проверку

0216 01F9 001026 000771 br @Loop

0218 0000 001030 000000 @Exit: halt

021A 6548 001032 062510 @Text: dw 'H' 'e'

021C 6C6C 001034 066154 dw 'l' 'l'

021E 2C6F 001036 026157 dw 'o' ','

0220 5720 001040 053440 dw ' ' 'W'

0222 726F 001042 071157 dw 'o' 'r'

0224 646C 001044 062154 dw 'l' 'd'

0226 0021 001046 000041 dw '!' 0

Запись команд mov, add и tst в восьмеричной системе счисления легко читается, чего нельзя сказать об их записи в шестнадцатеричной системе счисления. Команды переходов и текстовые строки легко читаются в шестнадцатеричной системе счисления и нечитаемы в восьмеричной.

Возможно, после вывода символа следует проверять отсутствие ошибок в работе телетайпа (бит 15 регистра статуса телетайпа).

8080

Предполагается использование операционной системы CP/M-80 (все программы проверены в эмуляторе MYZ80 1.24). CP/M загружает программу в область памяти с начальным адресом 0x100 и выполняет переход по адресу 0x100. Программа использует две функции CP/M - вывод символа (2) и завершение программы (0):

Адрес Код Метка Мнемоника

----- -------- ------ ---------

0100 0E 02 mvi C, 2 ;Вывод символа

0102 1E 48 mvi E, 'H'

0104 CD 05 00 call 5

0107 0E 02 mvi C, 2 ;Вывод символа

0109 1E 65 mvi E, 'e'

010B CD 05 00 call 5

....

015B 0E 00 mvi C, 0 ;Завершение программы

015D CD 05 00 call 5

Код имеет тот же недостаток, что и его прототип для PDP-11. Можно использовать функцию вывода строки, оканчивающейся символом $ (9):

Адрес Код Метка Мнемоника

----- -------- ------ ---------

0100 0E 09 mvi C, 9 ;Вывод строки

0102 11 0D 01 lxi D, @Text

0105 CD 05 00 call 5

0108 0E 00 mvi C, 0 ;Завершение программы

010A CD 05 00 call 5

010D 48 @Text: db 'H'

010E 65 db 'e'

010F 6C db 'l'

0110 6C db 'l'

0111 6F db 'o'

0112 2C db ','

0113 20 db ' '

0114 57 db 'W'

0115 6F db 'o'

0116 72 db 'r'

0117 6C db 'l'

0118 64 db 'd'

0119 21 db '!'

011A 24 db $

Наконец, можно использовать функцию вывода символа в цикле:

Адрес Код Метка Мнемоника

----- -------- ------ ---------

0100 21 1A 01 lxi H, @Text

0103 5E @Loop: mov E, M

0104 3E 00 mvi A, 0

0106 93 sub E

0107 CA 15 01 jz @Exit

010A E5 push H

010B 0E 02 mvi C, 2 ;Вывод символа

010D CD 05 00 call 5

0110 E1 pop H

0111 23 inx H

0112 C3 03 01 jmp @Loop

0115 0E 00 @Exit: mvi C, 0 ;Завершение программы

0117 CD 05 00 call 5

011A 48 @Text: db 'H'

011B 65 db 'e'

011C 6C db 'l'

011D 6C db 'l'

011E 6F db 'o'

011F 2C db ','

0120 20 db ' '

0121 57 db 'W'

0122 6F db 'o'

0123 72 db 'r'

0124 6C db 'l'

0125 64 db 'd'

0126 21 db '!'

0127 00 db 0

6502

Предполагается использование операционной системы Apple DOS (все программы проверены в эмуляторе AppleWin, образ диска был сформирован с помощью CiderPress). Программа должна загружаться в область памяти с начальным адресом 0x0C00 (3072), который является атрибутом файла(?). Для загрузки и запуска нужно ввести две команды:

BLOAD HELLOWORLD

CALL 3072

Программа использует одну функцию Apple DOS - вывод символа (ее адрес 0xFDF0):

Адрес Код Метка Мнемоника

----- -------- ------ ---------